GateGenerator

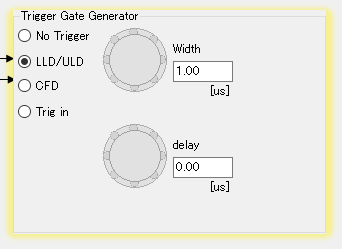

ゲートジェネレータは、LLDで発生したトリガ信号の、遅延や幅の拡張を行うためのものです。

ゲートジェネレータの入力はLLD/ULDからのトリガを使うか、CFDからのトリガを使うか、または外部入力を使うかを選択できます。

標準的な設定値

ソースはLLD/ULD、Widthは0~1us、delayは0usにしてください。

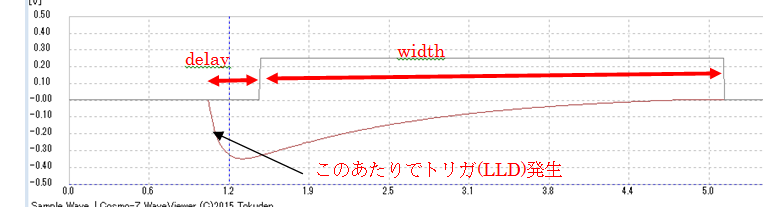

動作イメージ

DelayとWidthは下の図のようなイメージで動作します

LLDは信号の高さが閾値より大きくなるとトリガを発生しますが、このトリガの時間をdelayで示した量だけ遅延させ、widthの長さだけ引き延ばします。

実際にMCAや計測回路に送られるトリガはゲートの終了時となります。これはULDで指定された電圧以上のパルスが来た場合にトリガを無効化するため、LLDが解除されるまで待つためです。

widthを設定すると、短い時間に複数のイベントが発生したときに、後のイベントを無視させることができます。

用途

通常は使いません。原子核や素粒子の実験で、複数の検出器を使って複雑なゲート条件を作りたい場合に使います。

例えば、あるシンチレータ(装置全体の外側を包むなど)が何らかのイベントを検出し、その後、widthで指定した時間の間に発生するイベントはすべて無視する(VETO)といった用途で使います。粒子の飛行時間や、検出システム全体が麻痺するデッドタイムをdelayやwidthで指定することで、計測したくないイベントを除外することができます。